Makefile Tutorial

前言

本文翻译自https://makefiletutorial.com/#makefile-cookbook

我之所以编写这本指南,是因为我始终无法理解 Makefile。它们似乎充斥着隐藏的规则和深奥的符号,问一些简单的问题却得不到简单的答案。为了解决这个问题,我花了几个周末坐下来,阅读了所有关于 Makefile 的资料。我把最关键的知识浓缩到了这本指南中。每个主题都有简要说明和一个自带的示例,你可以自己运行。

如果你基本了解 Make,可以考虑查看 Makefile Cookbook,其中有一个中等规模项目的模板,对 Makefile 的每个部分的作用都有大量注释。

祝你好运,我希望你能战胜 Makefile 这个令人困惑的世界!

一. Getting Started

1.1 为什么需要Makefile

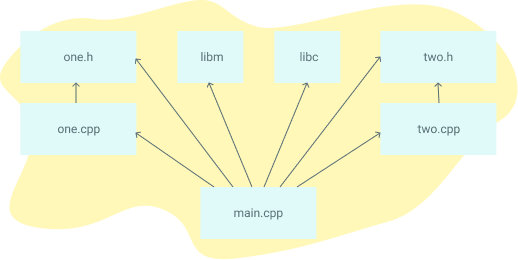

Makefile 用于帮助决定大型程序的哪些部分需要重新编译。在绝大多数情况下,编译的是 C 或 C++ 文件。其他语言通常也有自己的工具,其作用与 Make 类似。除了编译之外,Make 还可以用于根据文件变化运行一系列指令。本教程将重点介绍 C/C++ 编译用例。

下面是一个依赖关系图的示例,您可以用 Make 构建这个依赖关系图。如果任何文件的依赖关系发生变化,该文件将被重新编译:

1.2 除了Makefile还有什么其他选择

流行的 C/C++ 替代构建系统有 SCons、CMake、Bazel 和 Ninja。一些代码编辑器(如 Microsoft Visual Studio)也有自己的内置构建工具。Java 有 Ant、Maven 和 Gradle。其他语言(如 Go、Rust 和 TypeScript)也有自己的构建工具。

Python、Ruby 和原始 Javascript 等解释型语言不需要类似 Makefile 的工具。Makefile 的目标是根据已更改的文件编译需要编译的文件。但是,当解释型语言中的文件发生变化时,就不需要重新编译了。程序运行时,将使用文件的最新版本。

1.3 运行示例

要运行这些示例,你需要一个终端并安装 “make”。将每个示例的内容放入一个名为 Makefile 的文件中,然后在该目录下运行 make 命令。让我们从最简单的 Makefile 开始:

1 | hello: |

这里是运行后的输出:

1 | zrf@debian:/tmp$ make |

就是这样!如果你还有些困惑,这里有一段视频,详细介绍了这些步骤,以及 Makefile 的基本结构。

1.4 Makefile语法

Makefile 由一系列规则组成。规则一般是这样的

1 | targets: prerequisites |

- targets是文件名,以空格分隔。通常情况下,每条规则只有一个目标。

- command是用于创建targets的一系列步骤。这些命令需要以制表符开头,而不是空格。

- prerequisites(先觉条件)也是文件名,以空格分隔。在运行目标的命令之前,这些文件必须存在。这些文件也称为依赖项

1.5 Make的本质

让我们以hello world作为示例:

1 | hello: |

这里已经有很多东西需要了解。让我们来分解一下:

- 我们有一个名为 hello 的目标

- 这个目标有两个命令

- 该目标没有先决条件

然后运行 make hello。只要 hello 文件不存在,命令就会运行。如果 hello 文件存在,则不会运行任何命令。

要知道,我所说的 hello 既是目标,也是文件。这是因为两者直接联系在一起。通常情况下,当运行目标文件时(也就是运行目标文件的命令时),命令会创建一个与目标文件同名的文件。在当前的例子中,hello 目标并不会创建 hello 文件。

让我们创建一个更典型的 Makefile–一个编译单个 C 文件的 Makefile。在此之前,先创建一个名为 blah.c 的文件,其内容如下:

1 | // blah.c |

然后创建一个Makefile

1 | blah: |

这次,请尝试直接运行 make。由于 make 命令的参数中没有提供目标文件,因此会运行第一个目标文件。在本例中,只有一个目标(blah)。第一次运行时,blah 将被创建。第二次运行时,你会看到 make: ‘blah’ 是最新的。这是因为 blah 文件已经存在。但有一个问题:如果我们修改了 blah.c,然后运行 make,什么也不会重新编译。

为了解决修改源文件,目标文件不会重新编译的问题,我们为Makefile添加先觉条件:

1 | blah: blah.c |

当我们再次运行make时,会执行这些步骤

- 选择了第一个目标,因为第一个目标是默认目标

- 它的前提条件是 blah.c

- Make 决定是否运行 blah 目标。只有当 blah 不存在,或 blah.c 比 blah 新时,它才会运行

最后一步至关重要,是 make 的精髓所在。它要做的是判断自上次编译 blah 以来,blah 的先决条件是否发生了变化。也就是说,如果 blah.c 被修改了,运行 make 就应该重新编译该文件。反之,如果 blah.c 没有改变,则不应重新编译。

为了做到这一点,它会使用文件系统时间戳作为代理来判断是否有内容发生了更改。这是一种合理的启发式方法,因为文件时间戳通常只有在文件被修改时才会发生变化。但必须认识到,情况并非总是如此。例如,你可以修改一个文件,然后把该文件的修改时间戳改成旧的。如果你这样做了,Make 就会错误地认为该文件没有更改,从而忽略它。

请务必理解这一点。这是 Makefile 的关键所在,可能需要花几分钟时间才能正确理解。如果还是不明白,请参考上面的示例或观看上面的视频。

1.6 更多快速示例

下面的 Makefile 最终会运行所有三个目标。当你在终端运行 make 时,它会通过一系列步骤构建一个名为 blah 的程序:

- make 选择目标 blah,因为第一个目标是默认目标

- blah 需要 blah.o,所以 make 搜索 blah.o 目标

- blah.o 需要 blah.c,所以 make 会搜索 blah.c 目标

- blah.c 没有依赖关系,因此运行 echo 命令

- 然后运行 cc -c 命令,因为所有 blah.o 的依赖关系都已完成

- 运行 top cc 命令,因为所有 blah 的依赖关系都已完成

- 就是这样:blah 是一个编译过的 c 程序

1 | blah: blah.o |

如果删除 blah.c,所有三个目标都将重新运行。如果编辑它(从而将时间戳改为比 blah.o 新),则会运行前两个目标。如果运行 touch blah.o(从而将时间戳改为比 blah 更新),则只会运行第一个目标。如果什么都不改,则所有目标都不会运行。试试看

下一个示例没有做任何新内容,但仍然是一个很好的补充示例。它将始终运行两个目标,因为 some_file 依赖于 other_file,而 other_file 从未创建。

1 | some_file: other_file |

1.7 Make clean

clean 经常被用作删除其他目标的输出的目标,但它在 Make 中并不是一个特殊的词。你可以运行 make 和 make clean 来创建和删除 some_file。

请注意,clean在这里做了两件新事情:

它不是第一目标(默认),也不是先决条件。这意味着除非明确调用 make clean,否则它永远不会运行。

它不是一个文件名。如果你碰巧有一个名为 clean 的文件,这个目标就不会运行,这不是我们想要的。如何解决这个问题,请参见本教程后面的 .PHONY 部分

1 | some_file: |

1.8 变量

变量只能是字符串。通常要使用 :=,但 = 也可以。参见变量 Pt 2。

下面是一个使用变量的示例:

1 | files := file1 file2 |

单引号或双引号对 Make 没有任何意义。它们只是分配给变量的字符。不过,引号对 shell/bash 很有用,在 printf 等命令中需要用到它们。在本例中,两个命令的行为是一样的:

1 | a := one two # a is set to the string "one two" |

使用 ${} 或 $() 引用变量

1 | x := dude |

二. Target

2.1 all target

制作多个目标,并希望所有目标都运行?制作一个全部目标。由于这是列出的第一条规则,因此如果调用 make 而未指定目标,它将默认运行。

1 | all: one two three |

2.2 多目标

当一条规则有多个目标时,将针对每个目标运行命令。$@ 是一个自动变量,包含目标名称。

1 | all: f1.o f2.o |

三. 自动变量和通配符

3.1 * wildcard

在 Make 中,* 和 % 都被称为通配符,但它们的含义完全不同。* 在文件系统中搜索匹配的文件名。我建议你始终将其封装在wildcard函数中,否则你可能会陷入下面描述的一个常见陷阱。

1 | # Print out file information about every .c file |

* 可以在目标、先决条件或通配符功能中使用。

危险: * 不能在变量定义中直接使用。

危险:当 * 不能匹配任何文件时,它将保持原样(除非在通配符函数中运行)

1 | thing_wrong := *.o # Don't do this! '*' will not get expanded |

3.2 % Wildcard

% 确实很有用,但由于可用于多种情况,所以有点令人困惑。

- 在 “匹配” 模式下使用时,它会匹配字符串中的一个或多个字符。这种匹配称为词干。

- 在 “替换” 模式下使用时,它会将匹配到的词干替换到字符串中。

- % 通常用于规则定义和某些特定功能中。

3.3 自动变量

自动变量有很多,但往往只有少数几个会出现:

1 | hey: one two |

四. 规则

4.1 隐式规则

Make 中最令人困惑的部分可能是那些神奇的自动规则。Make 将这些规则称为 “隐含 “规则。我个人并不同意这一设计决定,也不建议使用它们,但它们经常被使用,因此了解它们很有用。下面是隐含规则的列表:

- 编译 C 程序:使用 $(CC) -c $(CPPFLAGS) $(CFLAGS) $^ -o $@ 形式的命令从 n.c 自动生成 n.o。

- 编译 C++ 程序:使用形式为 $(CXX) -c $(CPPFLAGS) $(CXXFLAGS) $^ -o $@ 的命令,可自动从 n.cc 或 n.cpp 生成 n.o

- 链接单个对象文件:通过运行 $(CC) $(LDFLAGS) $^ $(LOADLIBES) $(LDLIBS) -o $@ 命令,可从 n.o 自动生成 n

隐式规则使用的重要变量有:

- CC: 编译 C 程序的程序;默认为 cc

- CXX: 用于编译 C++ 程序的程序;默认为 g++

- CFLAGS:提供给 C 编译器的额外标志

- CXXFLAGS:提供给 C++ 编译器的额外标志

- CPPFLAGS:提供给 C 预处理器的额外标记

- LDFLAGS:在编译器调用链接器时提供给编译器的额外标记

让我们看看如何在不明确告诉 Make 如何编译的情况下编译 C 程序:

1 | CC = gcc # Flag for implicit rules |

4.2 静态模式规则

静态模式规则是在 Makefile 中减少编写内容的另一种方法,但我认为它更有用,而且不那么 “神奇”。下面是它们的语法:

1 | targets...: target-pattern: prereq-patterns ... |

其实质是通过目标模式(通过 % 通配符)匹配给定目标。匹配到的内容称为词干。然后将词干代入先决条件模式,生成目标的先决条件。

一个典型的用例是将 .c 文件编译成 .o 文件。下面是手动方法:

1 | objects = foo.o bar.o all.o |

下面是使用静态模式规则的更有效方法:

1 | objects = foo.o bar.o all.o |

4.3 静态模式规则和过滤器

在稍后介绍函数的同时,我将先介绍一下可以用它们做些什么。过滤器函数可用于静态模式规则,以匹配正确的文件。在本例中,我制作了 .raw 和 .result 扩展名。

1 | obj_files = foo.result bar.o lose.o |

4.4 Pattern Rules

Pattern Rules经常被使用,但却很容易混淆。您可以从两个方面来看待它们:

- 定义自己的隐式规则

- 一种更简单的静态模式规则

我们先来看一个例子:

1 | # Define a pattern rule that compiles every .c file into a .o file |

模式规则在目标中包含一个”%”。该’%’匹配任何非空字符串,其他字符则自行匹配。模式规则先决条件中的”%”代表与目标中的”%”匹配的同一词干。

4.5 双冒号规则

双冒号规则很少使用,但允许为同一目标定义多个规则。如果是单冒号,则会打印警告,并且只会运行第二组命令。

五. Commands and execution

5.1 命令行的输出/静默

在命令前添加 @ 以阻止命令被打印出来

您也可以使用 -s 运行 make,在每一行前添加 @

1 | all: |

5.2 命令行的执行

每条命令都在一个新的 shell 中运行(至少效果是这样的)

1 | all: |

5.3 默认shell

默认 shell 为 /bin/sh。你可以通过修改变量 SHELL 来改变它:

1 | SHELL=/bin/bash |

5.4 双美元符号

如果希望字符串带有美元符号,可以使用 $$。这就是如何在 bash 或 sh 中使用 shell 变量。

请注意 Makefile 变量和 Shell 变量之间的区别。

1 | make_var = I am a make variable |

5.5 使用 -k、-i 和 - 处理错误

运行 make 时添加 -k,即使出现错误也能继续运行。如果你想一次性看到 Make 的所有错误,这很有用。

在命令前添加 - 来抑制错误

在 make 中添加 -i 可让每条命令都出错。

1 | one: |

5.6 中断或杀死

请注意:如果按 ctrl+c ,它将删除刚刚make的新目标。

5.7 make 的递归使用

要递归调用 makefile,请使用特殊的 $(MAKE) 而不是 make,因为它会为你传递 make 标志,而自身不会受其影响。

1 | new_contents = "hello:\n\ttouch inside_file" |

5.8 导出、环境和递归 make

当 Make 启动时,它会自动从执行时设置的所有环境变量中创建 Make 变量。

1 | # Run this with "export shell_env_var='I am an environment variable'; make" |

The export directive takes a variable and sets it the environment for all shell commands in all the recipes:

1 | shell_env_var=Shell env var, created inside of Make |

因此,在 make 中运行 make 命令时,可以使用 export 指令使子 make 命令可以访问它。在本例中,cooly 被导出,以便子目录中的 makefile 可以使用它。

1 | new_contents = "hello:\n\techo \$$(cooly)" |

您还需要导出变量,以便在 shell 中运行。

1 | one=this will only work locally |

.EXPORT_ALL_VARIABLES 会为您导出所有变量。

1 | .EXPORT_ALL_VARIABLES: |

5.9 make的参数

有很多的选项列表,可以通过 make 运行。请查看–fry-run、–touch、–old=file。

你可以为 make 设置多个目标,例如,make clean run test 运行 clean 目标,然后运行,最后测试。

六. 变量 2

6.1 Flavors and modification

变量有两种:

- 递归(使用 =)–只在使用命令时查找变量,而不是在定义变量时。

- 简单扩展(使用 :=)–就像普通的命令式编程一样–只有到目前为止定义的变量才会被扩展

1 | # Recursive variable. This will print "later" below |

简单扩展(使用 :=)就可以追加到变量中。递归定义将导致无限循环错误。

1 | one = hello |

?= 仅设置尚未设置的变量

1 | one = hello |

行尾的空格不会被删除,但行首的空格会被删除。要使用单空格创建变量,请使用 $(nullstring)

1 | with_spaces = hello # with_spaces has many spaces after "hello" |

未定义变量实际上是一个空字符串!

1 | all: |

使用 += 来扩展

1 | foo := start |

字符串替换也是修改变量的一种非常常见和有用的方法。还可以查看文本函数和文件名函数。

6.2 命令行参数和覆盖

使用 override 可以覆盖命令行变量。在这里,我们使用 make option_one=hi 运行 make

1 | # Overrides command line arguments |

6.3 List of commands and define

define并不是一个函数,尽管它看起来像。我见过它的使用频率很低,所以就不细说了,但它主要用于定义canned recipes ,还能与 eval 函数很好地搭配使用。

define/endef 简单地创建一个变量,并将其设置为一系列命令。请注意,这与在命令之间使用分号有点不同,因为每个命令都会在单独的 shell 中运行。

1 | one = export blah="I was set!"; echo $$blah |

6.4 Target-specific variables

可为特定目标设置变量

1 | all: one = cool |

6.5 Pattern-specific variables

您可以为特定目标模式设置变量

1 | %.c: one = cool |

七. 条件判断

7.1 if/else

1 | foo = ok |

7.2 检查变量是否为空

1 | nullstring = |

7.3 检查变量是否已定义

ifdef 不会扩展变量引用;它只是查看是否定义了某个变量

1 | bar = |

7.4 $(MAKEFLAGS)

本例演示如何使用 findstring 和 MAKEFLAGS 测试 make 标志。使用 make -i 运行此示例,即可看到它打印出 echo 语句。

1 | all: |

八. 函数

8.1 First function

函数主要用于文本处理。使用 $(fn, arguments) 或 ${fn, arguments} 调用函数。Make 有大量内置函数。

1 | bar := ${subst not,totally, "I am not superman"} |

如果要替换空格或逗号,请使用变量

1 | comma := , |

在第一个参数之后的参数中不要包含空格。空格将被视为字符串的一部分。

1 | comma := , |

8.2 字符串替换

$(patsubst pattern,replacement,text) 执行以下操作:

“Finds whitespace-separated words in text that match pattern and replaces them with replacement. Here pattern may contain a ‘%’ which acts as a wildcard, matching any number of any characters within a word. If replacement also contains a ‘%’, the ‘%’ is replaced by the text that matched the ‘%’ in pattern. Only the first ‘%’ in the pattern and replacement is treated this way; any subsequent ‘%’ is unchanged.” (GNU docs)

替换引用 $(text:pattern=replacement) 就是这种情况的简写。

还有一种只替换后缀的速记方法:$(text:sufficiency=replacement)。这里不使用 % 通配符。

注意:不要为这种速记法添加额外的空格。它会被视为搜索或替换词。

1 | foo := a.o b.o l.a c.o |

8.3 循环函数

foreach 函数看起来像这样:$(foreach var,list,text).它将一个单词列表(用空格分隔)转换为另一个单词列表。var 设置为列表中的每个单词,text 则为每个单词扩展。

这会在每个单词后添加一个感叹号:

1 | foo := who are you |

8.4 if函数

if 检查第一个参数是否为非空。如果是,则运行第二个参数,否则运行第三个参数。

1 | foo := $(if this-is-not-empty,then!,else!) |

8.5 call函数

Make 支持创建基本函数。您只需通过创建一个变量来 “define” 函数,但要使用 $(0)、$(1) 等参数。然后使用特殊的调用内置函数调用该函数。语法是 $(调用变量,参数,param)。$(0)是变量,$(1)、$(2)等是参数。

1 | sweet_new_fn = Variable Name: $(0) First: $(1) Second: $(2) Empty Variable: $(3) |

8.6 shell函数

shell - 调用 shell,但会用空格替换换行符!

1 | all: |

九. 其他特性

9.1 包含 Makefile

include 指令告诉 make 读取一个或多个其他 makefile。这是 makefile 中的一行,看起来像这样:

1 | include filenames... |

这在使用 -M 等编译器标志时特别有用,这些标志会根据源代码创建 Makefile。例如,如果某些 c 文件包含一个头文件,那么该头文件就会被添加到由 gcc 编写的 Makefile 中。我将在 Makefile Cookbook 中详细介绍这一点

十. Makefile Cookbook

让我们来看看一个非常实用的 Make 示例,它非常适合中等规模的项目。

这个 makefile 最棒的地方在于它会自动为你确定依赖关系。你只需将 C/C++ 文件放入 src/ 文件夹即可。

1 | # Thanks to Job Vranish (https://spin.atomicobject.com/2016/08/26/makefile-c-projects/) |